Rangkaian Counter dengan J-K flip flop

1. Tujuan [Kembali]

mengetahui counter juga bisa dengan j-k flip flop

2. Alat dan bahan [Kembali]

Alat dan bahan yang digunakan yaitu :

a. Negative edge triggered J-K flip-flops

b. clock

c. Logicstate

d. Logic probe

e. Gerbang NAND

f.Seven segment

3. Teori [Kembali]

Counter merupakan suatu sistem yang digunakan untuk melakukan pencacahan data, dalam postingan ini akan dibahas tentang pembuatan rangkaian counter dengan menggunakan JKFF secara sinkron dan asinkron, perbedaan counter sinkron dengan asinkron adalah dari pemberian sumber detak rangkaiannya, jika counter sinkron maka pemberian detak untuk mengeluarkan data pada masing-masing JKFF dilakukan secara bersamaan, tetapi pada counter asinkron pemberian detak masing-masing JKFF dilakukan secara bergantian atau berantai.

4. Gambar Rangkaian dan Prinsip Kerja [Kembali]

1. Counter Up Sinkron Modul 16 dengan JKFF.

Yang pertama adalah rangkaian counter up sinkron, untuk rangkaian dibawah ini adalah rangkaian counter up sinkron modul 16 dengan JKFF (JK Flip-Flop).

|

| Counter Up Sinkron Modul 16 dengan JKFF |

|

| Counter Up Sinkron Modul 16 dengan JKFF |

dari rangkaian tersebut sudah dapat dilihat bahwasanya masing-masing JKFF mengeluarkan satu bit data, yang mana keseluruhan dari rangkaian ini jika dijumlahkan menjadi 4 bit data atau akan melakukan counter/pencacahan dari 0 hingga 15 dalam bilangan desimal, cara kerja dari rangkaian ini adalah ketika JKFF D0 diberikan clock akan mengeluarkan logika 1 sehingga jika diurutkan dari D3_D2_D1_D0 adalah biner 0001 (1 dalam desimal)selanjutnya keluaran JKFF D0 akan mempengaruhi masukan JKFF D1 sehingga mengeluarkan output 1, dan keluaran JKFF D0 menjadi 0 sehingga jika diurutkan dari D3_D2_D1_D0 adalah biner 0010 (2 dalam desimal) dan begitu selanjutnya untuk biner 0011 (3 dalam desimal) , sedangkan untuk menghidupkan/mengeluarkan bit selanjutnya yaitu keluaran JKFF D2 dibutuhkan gerbang logika "and" untuk mempengaruhi masukan JKFF D2 tetapi syaratnya D1 dan D0 harus 1 maka dari itu menggunakan gerbang "and" D1 berlogika 1 di "and" kan D0 yang berlogika 1 maka akan mengeluarkan output 1 dan dimasukkan kedalam masukan JKFF D2, sehingga saat dilakukan "clock" menghasilkan bit biner D3_D2_D1_D0 menjadi 0100 (3 dalam desimal) begitu seterusnya, sehingga untuk mempengaruhi masukan D3 pun membutuhkan rangkaian gerbang logika D0 and D1 and D2 seperti dalam gambar diatas.

2. Counter Down Sinkron Modul 8 dengan JKFF.

Selanjutnya adalah rangkaian counter down sinkron modul 8 dengan JKFF. rangkaiannya dapat dilihat dibawah ini :

|

| Tabel Kebenaran Counter Down Sinkron Modul 8 |

|

| Counter Down Sinkron Modul 16 dengan JKFF |

3. Counter Up Asinkron Modul 16 dengan JKFF.

Untuk rangkaian dibawah ini adalah counter up asinkron modul 16 dengan JKFF.

|

| Counter Up Asinkron Modul 16 |

|

| Counter Up Asinkron Modul 16 dengan JKFF |

4. Counter Down Asinkron Modul 16 dengan JKFF.

Untuk counter down asinkron modul 16 dengan JKFF dapat dilihat dibawah ini :

|

| Counter Down Asinkron Modul 16 dengan JKFF |

5. Counter Modul X Sinkron dengan JKFF.

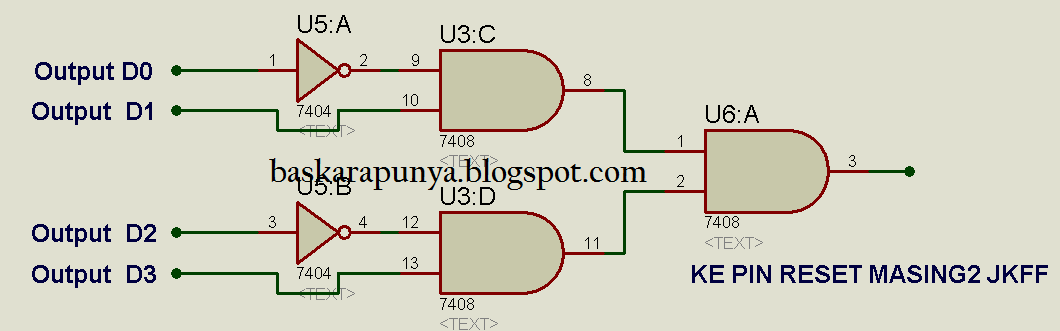

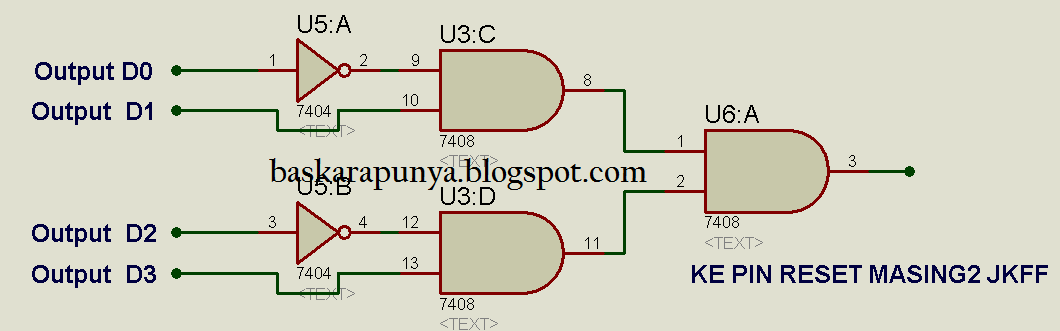

Counter modulo X merupakan suatu counter yang akan melakukan pencacahan hingga bit tertentu sesuai dengan yang diinginkan/dibutuhkan, misalkan apabila kita mempunyai 4 bit counter up sinkron dengan JKFF, berarti counter tersebut adalah modul 16 yang akan mencacah dari 0 hingga15 tetapi apabila kita hanya membutuhkan modul tertentu, misalkan modul 10 yang akan mencacah dari 0 hingga 9, seperti bila kita akan membuat detik dan menit satuan pada jam digital. Kita dapat menggunakan pin masukan "Reset" untuk mengatur supaya ketika pada bit tertentu akan kembali ke bit awal misalkan jika hanya akan mengcounter hingga 9 maka pada bit 1010 atau 10 ia harus kembali ke bit 0000 dan tidak akan menampilkan bit 1010. dibawah ini adalah rangkaian keseluruhan pada counter modulo 10 sinkron menggunakan JKFF.

|

| Tabel Kebenaran Counter Sinkron Modul X (10) |

|

| Counter Modul 10 Sinkron dengan JKFF |

|

| Rangkaian Logika untuk Reset |

6. Counter Up/Down Sinkron dengan JKFF.

Selanjutnya kita membahas tentang counter up/down sinkron dengan JKFF, kali ini saya membuat counter up/down sinkron modul 8 terlebih dahulu. jadi rangkaian ini mempunyai bit selector, apa itu bit selector? yaitu suatu masukkan bit yang akan digunakan sebagai pemilih dan pengatur apakah rangkaian akan menjadi counter up atau counter down. jadi didalam rangkaian keseluruhan counter up/down sinkron modul 8 mempunyai tiga sistem rangkaian utama, yaitu rangkaian counter itu sendiri yang terdiri dari JKFF, rangkaian logika pembuat pencacahan naik (gambar dibawah, gerbang and berada diatas JKFF), dan rangkaian logika pembuat pencacahan turun (gambar dibawah ini, gerbang and berada dibawah JKFF). Counter merupakan suatu sistem yang digunakan untuk melakukan pencacahan data, dalam postingan ini akan dibahas tentang pembuatan rangkaian counter dengan menggunakan JKFF secara sinkron dan asinkron, perbedaan counter sinkron dengan asinkron adalah dari pemberian sumber detak rangkaiannya, jika counter sinkron maka pemberian detak untuk mengeluarkan data pada masing-masing JKFF dilakukan secara bersamaan, tetapi pada counter asinkron pemberian detak masing-masing JKFF dilakukan secara bergantian atau berantai.

1. Counter Up Sinkron Modul 16 dengan JKFF.

Yang pertama adalah rangkaian counter up sinkron, untuk rangkaian dibawah ini adalah rangkaian counter up sinkron modul 16 dengan JKFF (JK Flip-Flop).

|

| Counter Up Sinkron Modul 16 dengan JKFF |

|

| Counter Up Sinkron Modul 16 dengan JKFF |

dari rangkaian tersebut sudah dapat dilihat bahwasanya masing-masing JKFF mengeluarkan satu bit data, yang mana keseluruhan dari rangkaian ini jika dijumlahkan menjadi 4 bit data atau akan melakukan counter/pencacahan dari 0 hingga 15 dalam bilangan desimal, cara kerja dari rangkaian ini adalah ketika JKFF D0 diberikan clock akan mengeluarkan logika 1 sehingga jika diurutkan dari D3_D2_D1_D0 adalah biner 0001 (1 dalam desimal)selanjutnya keluaran JKFF D0 akan mempengaruhi masukan JKFF D1 sehingga mengeluarkan output 1, dan keluaran JKFF D0 menjadi 0 sehingga jika diurutkan dari D3_D2_D1_D0 adalah biner 0010 (2 dalam desimal) dan begitu selanjutnya untuk biner 0011 (3 dalam desimal) , sedangkan untuk menghidupkan/mengeluarkan bit selanjutnya yaitu keluaran JKFF D2 dibutuhkan gerbang logika "and" untuk mempengaruhi masukan JKFF D2 tetapi syaratnya D1 dan D0 harus 1 maka dari itu menggunakan gerbang "and" D1 berlogika 1 di "and" kan D0 yang berlogika 1 maka akan mengeluarkan output 1 dan dimasukkan kedalam masukan JKFF D2, sehingga saat dilakukan "clock" menghasilkan bit biner D3_D2_D1_D0 menjadi 0100 (3 dalam desimal) begitu seterusnya, sehingga untuk mempengaruhi masukan D3 pun membutuhkan rangkaian gerbang logika D0 and D1 and D2 seperti dalam gambar diatas.

2. Counter Down Sinkron Modul 8 dengan JKFF.

Selanjutnya adalah rangkaian counter down sinkron modul 8 dengan JKFF. rangkaiannya dapat dilihat dibawah ini :

|

| Tabel Kebenaran Counter Down Sinkron Modul 8 |

|

| Counter Down Sinkron Modul 16 dengan JKFF |

3. Counter Up Asinkron Modul 16 dengan JKFF.

Untuk rangkaian dibawah ini adalah counter up asinkron modul 16 dengan JKFF.

|

| Counter Up Asinkron Modul 16 |

|

| Counter Up Asinkron Modul 16 dengan JKFF |

4. Counter Down Asinkron Modul 16 dengan JKFF.

Untuk counter down asinkron modul 16 dengan JKFF dapat dilihat dibawah ini :

|

| Counter Down Asinkron Modul 16 dengan JKFF |

5. Counter Modul X Sinkron dengan JKFF.

Counter modulo X merupakan suatu counter yang akan melakukan pencacahan hingga bit tertentu sesuai dengan yang diinginkan/dibutuhkan, misalkan apabila kita mempunyai 4 bit counter up sinkron dengan JKFF, berarti counter tersebut adalah modul 16 yang akan mencacah dari 0 hingga15 tetapi apabila kita hanya membutuhkan modul tertentu, misalkan modul 10 yang akan mencacah dari 0 hingga 9, seperti bila kita akan membuat detik dan menit satuan pada jam digital. Kita dapat menggunakan pin masukan "Reset" untuk mengatur supaya ketika pada bit tertentu akan kembali ke bit awal misalkan jika hanya akan mengcounter hingga 9 maka pada bit 1010 atau 10 ia harus kembali ke bit 0000 dan tidak akan menampilkan bit 1010. dibawah ini adalah rangkaian keseluruhan pada counter modulo 10 sinkron menggunakan JKFF.

|

| Tabel Kebenaran Counter Sinkron Modul X (10) |

|

| Counter Modul 10 Sinkron dengan JKFF |

|

| Rangkaian Logika untuk Reset |

6. Counter Up/Down Sinkron dengan JKFF.

Selanjutnya kita membahas tentang counter up/down sinkron dengan JKFF, kali ini saya membuat counter up/down sinkron modul 8 terlebih dahulu. jadi rangkaian ini mempunyai bit selector, apa itu bit selector? yaitu suatu masukkan bit yang akan digunakan sebagai pemilih dan pengatur apakah rangkaian akan menjadi counter up atau counter down. jadi didalam rangkaian keseluruhan counter up/down sinkron modul 8 mempunyai tiga sistem rangkaian utama, yaitu rangkaian counter itu sendiri yang terdiri dari JKFF, rangkaian logika pembuat pencacahan naik (gambar dibawah, gerbang and berada diatas JKFF), dan rangkaian logika pembuat pencacahan turun (gambar dibawah ini, gerbang and berada dibawah JKFF).

5. Video [Kembali]

6. Link download [Kembali]

gambar : download

rangkaian : download

video : download

Data sheet : download

html :download

Tidak ada komentar:

Posting Komentar