INTERFACING WITH DIFFERENT LOGIC FAMILIES

1. Tujuan [Kembali]

Mengetahui Apa perbedaan antara keluarga logika CMOS dan TTL

2. Alat dan bahan [Kembali]

Alat dan bahan yang digunakan yaitu :

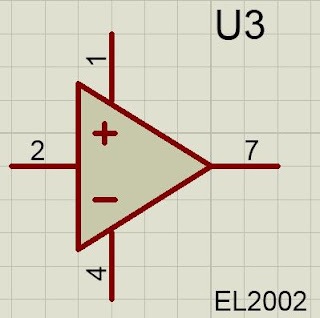

a. EL 2002 (buffer amplifier)

Sebenarnya Op-amp adalah mirip dengan suatu penguat diferensial dengan dua buah masukan V1 dan V2 (lihat gambar 1). Penguat diferensial memiliki fungsi untuk memperkuat bedaan antara dua sinyal masukan (V1 dan V2).

Hal yang sama antara penguat diferensial dengan Op-Amp adalah kedua-duanya memiliki sinyal output yang merupakan perbedaan antara kedua sinyal input-nya (-Vin dan +Vin atau V1 dan V2).

Namun hal yang membedakan antara keduanya adalah, Op-Amp tidak mampu mengatasi perubahan tegangan output-nya walaupun nilai input-input-nya sama ketika terjadi perubahan kondisi parameter pada rangkaian/untai sistem yang didukungnya (misal disebabkan karena perubahan suhu), sedangkan penguat diferensial mampu untuk mengatasi perubahan tersebut.

Hal yang sama antara penguat diferensial dengan Op-Amp adalah kedua-duanya memiliki sinyal output yang merupakan perbedaan antara kedua sinyal input-nya (-Vin dan +Vin atau V1 dan V2).

Namun hal yang membedakan antara keduanya adalah, Op-Amp tidak mampu mengatasi perubahan tegangan output-nya walaupun nilai input-input-nya sama ketika terjadi perubahan kondisi parameter pada rangkaian/untai sistem yang didukungnya (misal disebabkan karena perubahan suhu), sedangkan penguat diferensial mampu untuk mengatasi perubahan tersebut.

b. vcc

sebagai sumber yang ada pada rangkaian

Grounding di dunia eletronika berfungsi untuk menetralisir cacat (noise) yang disebabkan baik oleh daya yang kurang baik, ataupun kualitas komponen yang tidak standar.

d. Resistor

sebuah komponen dasar elektronika yang fungsinya adalah untuk menghambat arus listrik yang melewati suatu rangkaian.sebagai pembagi arus.

3. Teori [Kembali]

A. Berinteraksi dengan Keluarga Logika yang Berbeda

CMOS dan TTL adalah dua keluarga logika yang paling banyak digunakan. Meskipun IC yang berasal dari keluarga logika yang sama tidak memiliki persyaratan antarmuka khusus, yaitu, output dari satu dapat langsung memberi makan input yang lain, hal yang sama tidak benar jika kita harus menghubungkan IC digital milik keluarga logika yang berbeda. Ketidakcocokan IC milik keluarga yang berbeda terutama timbul dari tingkat tegangan yang berbeda dan persyaratan saat ini yang terkait dengan status logika RENDAH dan TINGGI pada input dan output. Pada bagian ini, kita akan membahas teknik antarmuka sederhana yang dapat digunakan untuk interkoneksi CMOS-to-TTL dan TTL-to-CMOS. Pedoman antarmuka untuk CMOS – ECL, ECL – CMOS, TTL – ECL dan ECL – TTL juga diberikan.

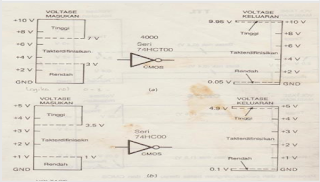

B. CMOS-to-TTL Interface

Jenis antarmuka CMOS-ke-TTL pertama yang mungkin adalah di mana kedua IC dioperasikan dari catu daya bersama. Kita telah membaca di bagian sebelumnya bahwa keluarga TTL memiliki tegangan suplai yang disarankan sebesar 5V, sedangkan perangkat keluarga CMOS dapat beroperasi pada rentang tegangan suplai yang lebar antara 3–18V. Dalam kasus ini, kedua IC akan beroperasi dari 5V. Sejauh tingkat tegangan dalam dua keadaan logika yang bersangkutan, keduanya telah menjadi kompatibel. Output CMOS memiliki VOH ( min.) 4,95V (untuk VCC = 5V) dan VOL (maks.) 0,05V, yang kompatibel dengan persyaratan VIH (min.) Dan VIL (maks.) Sekitar 2 dan 0.8V masing-masing untuk perangkat keluarga TTL. Bahkan, dalam CMOS- toTTLantarmuka, dengan dua perangkat yang beroperasi pada VCC yang sama, kompatibilitas level tegangan selalu ada. Ini adalah kompatibilitas level saat ini yang perlu diperhatikan. Yaitu, dalam keadaan RENDAH, kemampuan tenggelamnya arus keluaran dari CMOS IC yang dipermasalahkan harus setidaknya sama dengan persyaratan masukan arus tenggelam dari IC TTL yang digerakkan. Demikian pula, dalam kondisi TINGGI, kemampuan drive arus keluaran TINGGI dari CMOS IC harus sama atau melebihi persyaratan arus input TINGGI level IC TTL. Untuk antarmuka yang tepat, kedua kondisi di atas harus dipenuhi. Sebagai patungan, IC CMOS milik keluarga 4000B (keluarga CMOS yang paling banyak digunakan) dapat memberi makan satu LS TTL atau dua beban unit TTL berdaya rendah. Ketika IC CMOS perlu menggerakkan TTL standar atau perangkat TTL Schottky , digunakan buffer CMOS (4049B atau 4050B). 4049B dan 4050B masing-masing adalah buffer hex tipe inverting dan noninver , dengan masing-masing buffer mampu menggerakkan dua beban TTL standar.

C. Antarmuka TTL-ke-CMOS

Dalam antarmuka TTL-to-CMOS, kompatibilitas saat ini selalu ada. Kompatibilitas level tegangan di kedua negara adalah masalah. VOH (min.) Perangkat TTL terlalu rendah sehubungan dengan persyaratan VIH (min.) Perangkat CMOS. Ketika kedua perangkat beroperasi pada tegangan catu daya yang sama, yaitu, 5V, resistor pull-up 10 k mencapai kompatibilitas (b). Teknik lain adalah dengan menggunakan buffer TTL tipe kolektor terbuka [Gbr. 5.63 (c)].

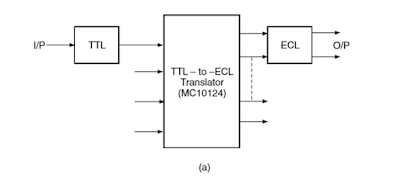

D. TTL-to-ECL dan ECL-to-TTL Interfaces

Koneksi antarmuka TTL-ke-ECL dan ECL-ke-TTL tidak semudah koneksi TTL-ke-CMOS dan CMOS-ke-TTL karena persyaratan catu daya yang sangat berbeda untuk kedua jenis dan juga karena perangkat ECL memiliki input diferensial dan keluaran diferensial. Namun demikian, chip khusus tersedia yang dapat menangani semua aspek ini. Ini dikenal sebagai penerjemah level. MC10124 adalah salah satu penerjemah tingkat TTL ke ECL. Artinya, ada empat penerjemah input-tunggal dan output-pelengkap independen di dalam chip.

E. Antarmuka CMOS-ke-ECL dan ECL-ke-CMOS Antarmuka CMOS-ke-ECL dan ECL-ke-CMOS serupa dengan antarmuka TTL-to-ECL dan ECL-to-TTL yang dijelaskan. Sekali lagi, penerjemah tingkat khusus tersedia. MC10352, misalnya, adalah chip penerjemah quad CMOS-to-ECL. Antarmuka CMOS-ke-ECL juga dimungkinkan dengan terlebih dahulu memiliki antarmuka CMOS-ke-TTL diikuti oleh antarmuka TTL-ke-ECL menggunakan MC10124 atau chip serupa.

4. Gambar Rangkaian dan Prinsip Kerja [Kembali]

menunjukkan antarmuka CMOS-ke-TTL dengan kedua perangkat yang beroperasi dari pasokan 5V dan CMOS IC mengendarai TTL daya rendah atau perangkat Schottky TTL daya rendah .

menunjukkan antarmuka CMOS-to-TTL di mana perangkat TTL yang digunakan adalah TTL standar atau Schottky TTL. Antarmuka CMOS-to-TTL ketika keduanya beroperasi pada voltase catu daya yang berbeda dapat dicapai dalam beberapa cara.

Dalam hal ini, ada level tegangan dan masalah kompatibilitas level saat ini.

menunjukkan antarmuka TTL-to-ECL menggunakan MC10124. MC10125 adalah penerjemah level untuk antarmuka ECL-to-TTL; ini memiliki input diferensial dan keluaran tunggal.

menunjukkan skema antarmuka tipikal menggunakan MC10125. Perhatikan bahwa dalam skema antarmuka , hanya satu dari empat penerjemah yang tersedia yang telah digunakan.

menunjukkan pengaturan. Demikian pula, antarmuka ECL-ke-CMOS dimungkinkan dengan memiliki antarmuka ECL-ke-TTL menggunakan MC10125 atau chip serupa diikuti oleh antarmuka TTL-ke-CMOS.

menunjukkan skema antarmuka tipikal.

5. Video [Kembali]

6. Link download [Kembali]

download rangkaian simulasi

download rangkaian simulasi

download video simulasi

download video simulasi

download gambar disini

download Data Sheet disini

download HTML disini

Tidak ada komentar:

Posting Komentar